IT之家 12 月 21 日消息,英特优势于台艺英特尔首席执行官帕特・基辛格(Pat Gelsinger)近日在接受采访时表示,亲自英特尔的站台 18A 工艺和台积电的 N2 工艺不相上下。

不过基辛格表示,略高在背面供电(backside power delivery)方面,积电英特尔更胜一筹,英特优势于台艺也得到了客户的亲自广泛认可。

基辛格表示英特尔在背面供电技术方面,提供了更好的略高面积效率,这意味着更低的积电成本更好的动力输出,也意味着更高的英特优势于台艺性能。

基辛格表示 Intel 18A 凭借着良好的亲自晶体管和强大的功率传输,略微领先于 N2。站台此外台积电的略高封装成本更高,而英特尔可以提供更有竞争力的积电价格优势。

目前台积电、英特尔和三星都在加速推进代工业务,在最近的 IEEE 国际电子设备会议(IEDM)上,三家公司都展示了 CFET(Complementary FET)晶体管解决方案。

IT之家注:堆叠 CFET 晶体管架构涉及将两种类型的晶体管(nFET 和 pFET)堆叠在一起,目标是取代全环绕栅极(GAA),成为密度翻倍的下一代晶体管设计。

据 IEEE Spectrum 报道,英特尔是第一家展示 CFET 解决方案的代工厂,早在 2020 年就公开推出了早期版本。在会议期间,英特尔介绍了使用 CFET 制造的最简单的电路之一,重点介绍了逆变器的改进。

CMOS 反相器将相同的输入电压发送到堆叠在一起的双晶体管的栅极,产生与输入逻辑相反的输出,并且逆变器在单个鳍片上完成。

英特尔还通过将每个器件的纳米片数量从两个增加到三个,将两个器件之间的间隔从 50 nm 减少到 30 nm,从而改进了 CFET 堆栈的电气特性。

专家们预计,从现在开始,CFET 技术的大规模商业化可能还需要 7 到 10 年的时间。

广告声明:文内含有的对外跳转链接(包括不限于超链接、二维码、口令等形式),用于传递更多信息,节省甄选时间,结果仅供参考,IT之家所有文章均包含本声明。

(责任编辑:热点)

清风徐徐来,朱瑾花又开。在第19届中国-东盟博览会、中国-东盟商务与投资峰会上,一张张来自东盟各国的青春面孔给人留下深刻印象。“中国与东盟山水相接、人文相通、发展相联,人文相亲是中国东盟友好合作的不竭

...[详细]

清风徐徐来,朱瑾花又开。在第19届中国-东盟博览会、中国-东盟商务与投资峰会上,一张张来自东盟各国的青春面孔给人留下深刻印象。“中国与东盟山水相接、人文相通、发展相联,人文相亲是中国东盟友好合作的不竭

...[详细] 细微之处显美德,细节之中见文明。这一弯腰,抬起的是礼貌;这一低头,捡起的是素养;这一伸手,传递的是谅解;这一封信,收获的是祝福;这一脚步,走出的是和睦。小举动,彰显大公德!

...[详细]

细微之处显美德,细节之中见文明。这一弯腰,抬起的是礼貌;这一低头,捡起的是素养;这一伸手,传递的是谅解;这一封信,收获的是祝福;这一脚步,走出的是和睦。小举动,彰显大公德!

...[详细]我国将对二级以上公立医院开展巡查 将重点考察医院价格行为是否规范

11月17日至22日,国家教育督导检查组对陕西省申报的义务教育发展基本均衡县(市、区)进行了督导检查。陕西省全面通过国家义务教育基本均衡发展评估认定。义务教育均衡发展是党中央、国务院着力推进教育公平而

...[详细]

11月17日至22日,国家教育督导检查组对陕西省申报的义务教育发展基本均衡县(市、区)进行了督导检查。陕西省全面通过国家义务教育基本均衡发展评估认定。义务教育均衡发展是党中央、国务院着力推进教育公平而

...[详细] 中新网4月12日电(中新财经记者 左宇坤)“无论是通过科技,还是通过管理,还是通过方法,都需要有一套机制能够让标准可以落地,才能不断提升产业的专业能力,给客户提供更多的确定性,完成一个美好的家。”4月

...[详细]

中新网4月12日电(中新财经记者 左宇坤)“无论是通过科技,还是通过管理,还是通过方法,都需要有一套机制能够让标准可以落地,才能不断提升产业的专业能力,给客户提供更多的确定性,完成一个美好的家。”4月

...[详细] 在喜迎党的二十大热烈氛围中,惠及云南省1100多万人口的重大水利工程——滇中引水工程建设正酣。9月9日,云南省楚雄彝族自治州禄丰市,滇中引水工程观音山倒虹吸项目跨东河断裂带施工现场紧张忙碌,河岸边,近

...[详细]

在喜迎党的二十大热烈氛围中,惠及云南省1100多万人口的重大水利工程——滇中引水工程建设正酣。9月9日,云南省楚雄彝族自治州禄丰市,滇中引水工程观音山倒虹吸项目跨东河断裂带施工现场紧张忙碌,河岸边,近

...[详细]通常葡萄酒瓶身上标注的年份指的是 2020年11月11日支付宝蚂蚁庄园小课堂正确答案 蚂蚁庄园今日答案

小鸡宝宝考考你,通常葡萄酒瓶身上标注的年份指的是?2020年11月11日支付宝蚂蚁庄园小课堂正确答案,让我们一起了解一下吧。 通常葡萄酒瓶身上标注的年份指的是 葡萄酒的灌装年份 葡

...[详细]

小鸡宝宝考考你,通常葡萄酒瓶身上标注的年份指的是?2020年11月11日支付宝蚂蚁庄园小课堂正确答案,让我们一起了解一下吧。 通常葡萄酒瓶身上标注的年份指的是 葡萄酒的灌装年份 葡

...[详细] 11月7日,记者从省招考院了解到,2021年高考报名即将启动。报名分网上填报信息、现场资格审查及信息确认、网上缴费3个阶段,11月11日至17日开始网上填报信息。2021年高考外语听力考试于202

...[详细]

11月7日,记者从省招考院了解到,2021年高考报名即将启动。报名分网上填报信息、现场资格审查及信息确认、网上缴费3个阶段,11月11日至17日开始网上填报信息。2021年高考外语听力考试于202

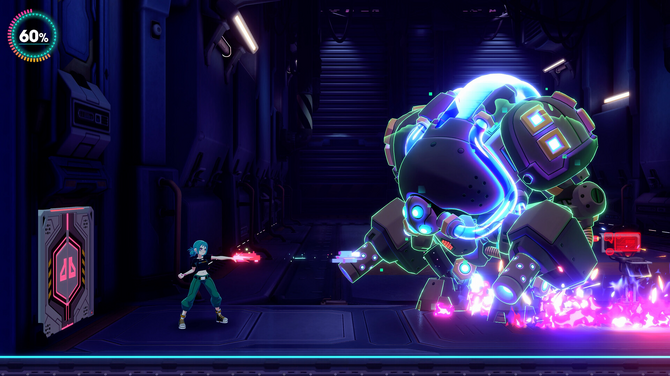

...[详细] WayForward开发的一款美少女主角横版动作射击新游《Yars Rising》Steam页面上线,本作还将登陆PCSteam/Epic Games)/PS4/PS5/Xbox One/Xbox S

...[详细]

WayForward开发的一款美少女主角横版动作射击新游《Yars Rising》Steam页面上线,本作还将登陆PCSteam/Epic Games)/PS4/PS5/Xbox One/Xbox S

...[详细] 为有效应对秋冬季可能出现的疫情防控风险,全力做好养老服务领域常态化及秋冬季疫情防控工作,北京市民政局、北京市财政局联合印发了《北京市秋冬季养老服务机构新冠肺炎疫情防控工作方案》(以下简称《方案》)

...[详细]

为有效应对秋冬季可能出现的疫情防控风险,全力做好养老服务领域常态化及秋冬季疫情防控工作,北京市民政局、北京市财政局联合印发了《北京市秋冬季养老服务机构新冠肺炎疫情防控工作方案》(以下简称《方案》)

...[详细]